Компоненты компьютерного железа

Базовое железо

Самое важное – материнская плата, это и есть компьютер, главная печатная плата, которая соединяет все компоненты между собой, обеспечивает питание и управление устройствами.

Материнская плата — это как центральный вокзал большого города. Поезда (данные) прибывают и отправляются на разные направления: к процессору, к памяти, к диску, к монитору. Железнодорожные пути — это дорожки на плате. Диспетчерская вышка — чипсет. Без вокзала поезда не смогут ни прибыть, ни отправиться, даже если сами локомотивы и вагоны исправны.

Её ключевые компоненты:

- Чипсет (Chipset) – диспетчер данных между CPU, RAM и периферией;

- Сокет (Socket) – разъем для процессора;

- Слоты RAM (ОЗУ) – разъём для оперативной памяти;

- PCIe-слоты для видеокарт, NVMe-дисков, Wi-Fi адаптеров;

- M.2 – разъём для NVMe-дисков;

- SATA – разъём для HDD и SSD;

- VRM (Voltage Regulator Module) – преобразователь напряжения для CPU;

- BIOS/UEFI – мини-операционная система для настройки железа, разгона устройств, включения и отключения компонентов;

- USB, HDMI, DisplayPort, Ethernet и аудио (3.5mm) разъемы для периферии.

★ Процессор (ЦП, CPU):

- выполняет инструкции программ (именно он отвечает за вычисления, счеты, сравнения и прочее);

- тактовая частота обозначает количество операций в секунду;

- ядра – единицы «работников-вычислителей»;

- кэш-память – временное хранилище для быстрого доступа к данным.

★ Оперативная память (RAM, ОЗУ):

- выполняет роль временного хранилища для программ и данных;

- быстрее даже самого быстрого диска SSD;

- при выключении память стирается – потому память временная;

- объем памяти – характеристика, обозначающая максимальный размер временного хранилища;

- частота – количество операций в секунду.

То есть, всё подключается в материнскую плату.

Это, в принципе, база.

А теперь поехали погружаться.

Компьютер — строго организованная иерархическая система, в которой каждый компонент выполняет строго определённую роль, а взаимодействие между ними регулируется аппаратными и логическими протоколами. Материнская плата (motherboard, mainboard) — это физическая и логическая основа такой системы. Она представляет собой многослойную печатную плату, на которой реализована топология шин, схемы управления питанием, логика маршрутизации сигналов и интерфейсы сопряжения. Без неё остальные компоненты остаются несвязанными «островами» — даже если физически подключить процессор к памяти напрямую, система не сможет инициировать загрузку, поскольку отсутствует управляющая логика инициализации, синхронизации и передачи данных.

Материнская плата — это аппаратный эквивалент операционной системы: она отвечает за жизненный цикл компьютера до момента передачи управления загрузчику. Её проектирование — компромисс между совместимостью, производительностью, расширяемостью и стоимостью. Архитектура платы определяет то, какие компоненты можно установить сегодня, и как система будет развиваться в ближайшие годы.

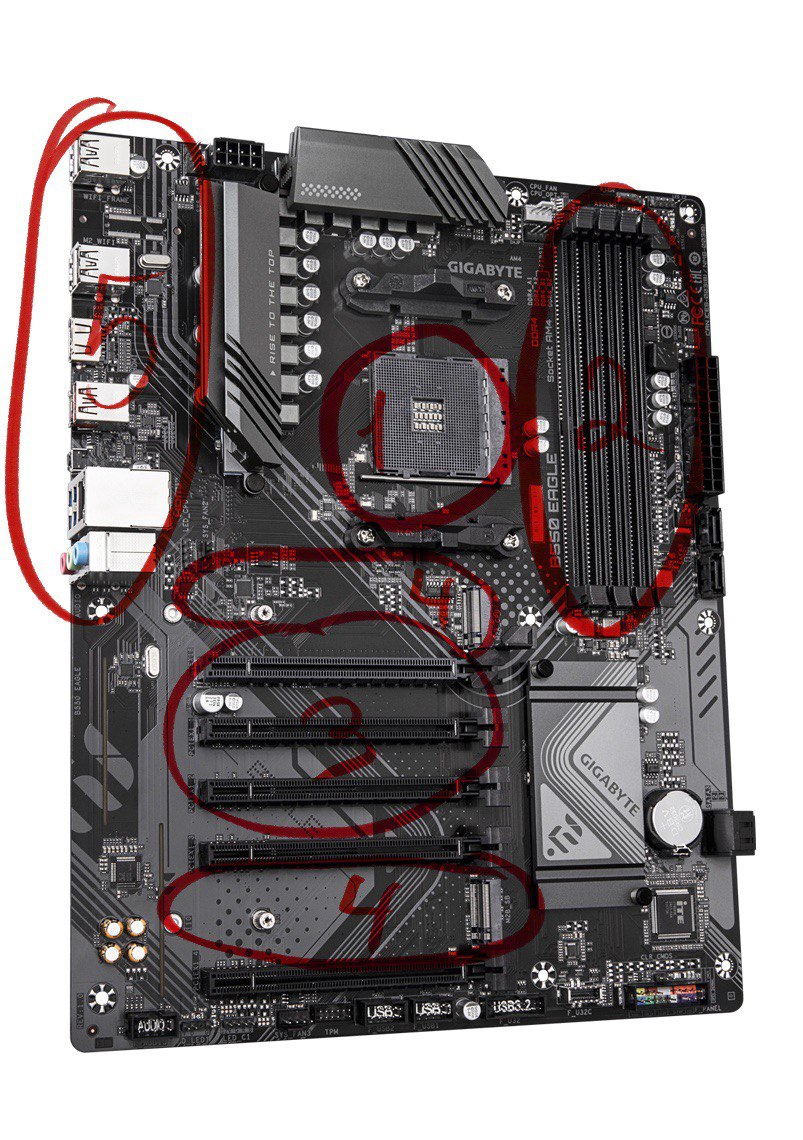

На изображении выше - как раз материнская плата, которую можно встретить в большинстве компьютеров. К примеру, там мы можем увидеть ключевые отделения:

- Сокет для процессора;

- Слоты для оперативной памяти;

- PCI-слоты для дополнительных устройств, например, для видеокарт;

- M.2-слоты для SSD;

- USB, Ethernet, и прочие порты для периферийных устройств.

Технически, материнская плата и является компьютером. Отличаются они набором возможностей, слотами и форматами.

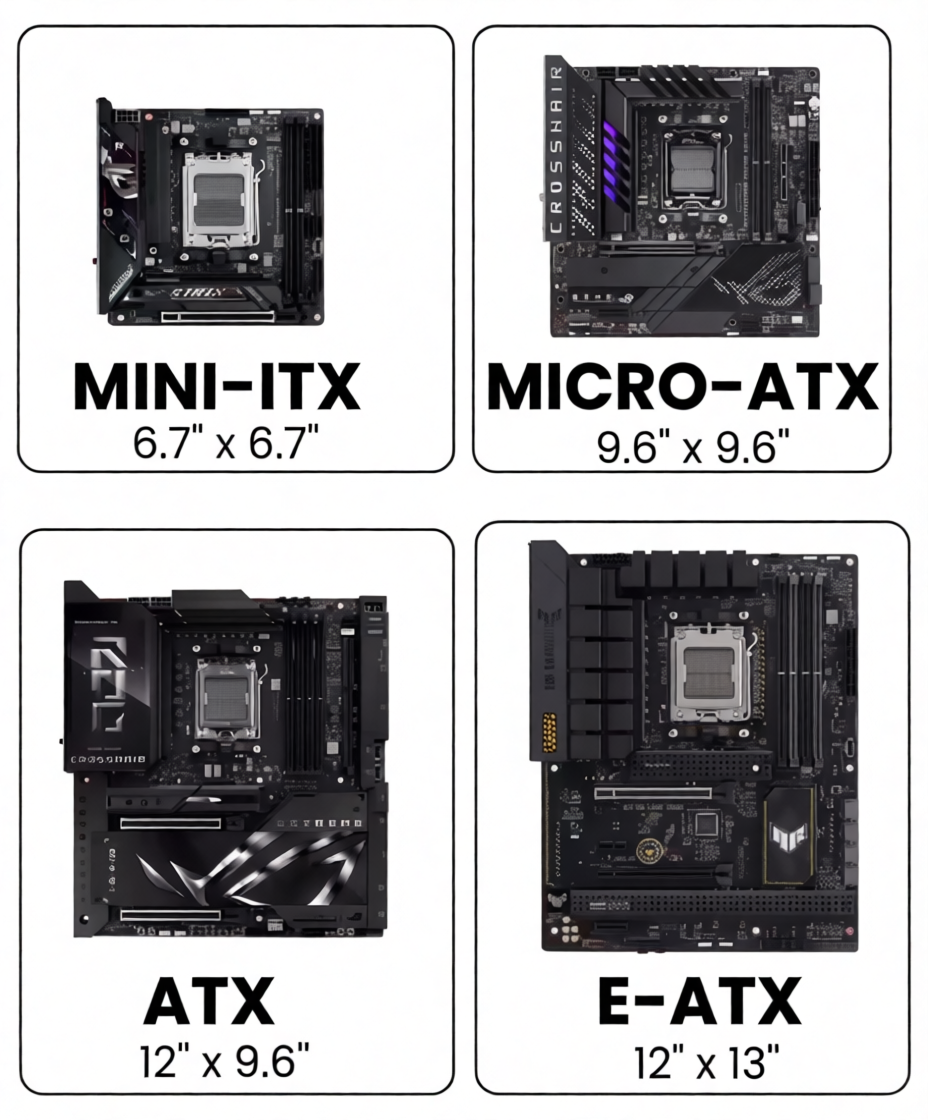

Различают Mini-ATX (самая маленькая), Micro-ATX, ATX и E-ATX размеры материнских плат.

| Форм-фактор | Размеры, мм | Количество слотов расширения | Типичное применение |

|---|---|---|---|

| Mini-ITX | 170 × 170 | 1 | Компактные ПК, HTPC, встраиваемые системы |

| Micro-ATX | 244 × 244 | До 4 | Бюджетные и средние настольные системы |

| ATX | 305 × 244 | До 7 | Стандартные настольные компьютеры |

| E-ATX | 305 × 330 | До 8 и более | Рабочие станции, игровые системы, серверы |

Дополнительные форм-факторы для специализированных решений:

| Форм-фактор | Размеры, мм | Особенности применения |

|---|---|---|

| FlexATX | 229 × 191 | Сверхкомпактные системы с ограниченным функционалом |

| SSI CEB | 305 × 267 | Корпоративные рабочие станции |

| SSI EEB | 305 × 330 | Высокопроизводительные серверы |

| XL-ATX | 325 × 280 | Экстремальные игровые платформы с расширенным охлаждением |

Соответственно, материнская плата со всеми остальными компонентами, помещается в единый корпус. Большая материнская плата требует большого корпуса (наряду и с дополнительными крупными элементами, например, видеокарта и жесткие диски). Размеры корпусов называют "башнями" - SFX, Mini-Tower, Mid-Tower, Full-Tower.

| Тип корпуса | Поддерживаемые форм-факторы |

|---|---|

| Full Tower | ATX, E-ATX, XL-ATX, Micro-ATX, Mini-ITX |

| Mid Tower | ATX, Micro-ATX, Mini-ITX |

| Mini Tower | Micro-ATX, Mini-ITX |

| Desktop | Micro-ATX, Mini-ITX |

| SFF | Mini-ITX, FlexATX |

1. Чипсет

Отмечу - чипсет, кстати, не является материнской платой. Это её главный элемент, некий логистический центр, управляющий обменом данными между процессором, оперативной памятью, видеокартой и накопителями. Чипсет — это 1–2 микросхемы (обычно под радиатором), а материнская плата — это вся печатная плата с разъемами.

Чипсет — это интегральная схема (или набор схем), реализующая функции южного и северного мостов (в классической архитектуре) или, в современных системах, Platform Controller Hub (PCH) в связке с встроенным в процессор Memory Controller Hub (MCH). Термин «чипсет» устарел в буквальном смысле — в процессорах Intel начиная с архитектуры Sandy Bridge (2011) и AMD с Zen (2017) функции северного моста (в первую очередь, контроллер памяти и PCIe-контроллер первого уровня) перенесены внутрь CPU. Однако осталась потребность в системном контроллере, обеспечивающем взаимодействие с периферийными устройствами.

| Блок | Основные функции | Современная реализация |

|---|---|---|

| Северный мост | Контроллер оперативной памяти, интерфейс процессора, шина AGP/PCIe для видеокарты | Интеграция в кристалл процессора (встроенный контроллер памяти и первичные линии PCIe) |

| Южный мост | Контроллеры SATA, USB, аудио, сетевой адаптер, шина PCI, LPC для прошивки | Отдельная микросхема Platform Controller Hub (PCH) или Fusion Controller Hub (FCH) |

Примеры чипсетов для настольных платформ:

| Производитель | Платформа | Модель чипсета | Год выпуска | Ключевые особенности |

|---|---|---|---|---|

| Intel | LGA 1155 | Z68, H67, P67 | 2011 | Поддержка процессоров Sandy Bridge, первое поколение с интегрированным контроллером памяти |

| Intel | LGA 1200 | Z490, B460, H410 | 2020 | Поддержка шины DMI 3.0, до 24 линий PCIe 3.0 в PCH |

| Intel | LGA 1700 | Z690, B660, H610 | 2021 | Разделение линий на PCIe 4.0 и 5.0, интеграция контроллера памяти DDR5 |

| AMD | AM4 | X570, B550, A520 | 2019–2020 | PCIe 4.0 в южном мосту, до 16 линий для видеокарты |

| AMD | AM5 | X670E, B650E, B650 | 2022 | Поддержка DDR5, до 28 линий PCIe 5.0, двухчиповая компоновка для флагманских моделей |

В современных платформах чипсет — это именно PCH, который:

- реализует низкоскоростные и среднескоростные интерфейсы: SATA, USB 2.0/3.x, LPC (Low Pin Count), SPI (для BIOS/UEFI), аудио (HDA — High Definition Audio), Ethernet (часто через интегрированный PHY), а также управление вентиляторами и датчиками температуры;

- предоставляет дополнительные линии PCIe (обычно поколения ниже, чем у CPU: например, CPU даёт PCIe 5.0 x16 для видеокарты, а чипсет — PCIe 4.0 x4 для M.2 или сетевых адаптеров);

- выступает посредником в арбитраже доступа к шине: когда несколько устройств одновременно запрашивают передачу данных (например, SSD и Wi-Fi), чипсет разрешает конфликты, распределяя пропускную способность шины DMI (Direct Media Interface у Intel) или Infinity Fabric Link у AMD;

- обеспечивает резервирование и изоляцию: сбой в USB-контроллере не должен приводить к остановке работы CPU или памяти — чипсет физически и логически разделяет домены питания и сигнализации.

Чипсет — интеллектуальный маршрутизатор данных. Его пропускная способность (например, DMI 4.0 ×8 у Intel 700-й серии — ~16 ГБ/с) часто становится узким местом в системах с множеством высокоскоростных NVMe-дисков, подключённых через чипсет, а не напрямую к процессору.

2. Сокет процессора

Сокет — стандартизированный многоконтактный разъём*, обеспечивающий:

- механическую фиксацию CPU (обычно через поворотный рычаг — retention mechanism);

- электрическое соединение между контактами процессора и трассировкой платы (каждый контакт — отдельная линия сигнала, питания или земли);

- совместимость в рамках поколения (например, сокет LGA 1700 поддерживает процессоры Intel 12‑го, 13‑го и 14‑го поколений, но не 11‑го или 15‑го — из-за изменения расположения контактов и требований VRM).

Количество контактов (pin count) определяется сложностью интерфейса: для современных x86-процессоров оно превышает 1700 (LGA 1700 — 1700 контактов на плате, 1800+ на процессоре, т.к. часть контактов — «пустые» для механической стабильности). Каждая группа контактов отвечает за определённую функцию:

- линии питания ядер (VCCCORE) и кэша (VCCGT);

- линии тактового генератора (BCLK);

- линии PCIe (для связи с видеокартой и NVMe);

- линии DMI/Infinity Fabric (к чипсету);

- линии управления (PROCHOT#, SVID, SMBus для VRM).

| Группа контактов | Назначение | Примеры сигналов и протоколов |

|---|---|---|

| Питание вычислительных блоков | Подача напряжения на ядра процессора и кэш-память | VCCCORE (ядра), VCCGT (графическое ядро и кэш), VID (цифровой интерфейс управления напряжением) |

| Тактовые сигналы | Синхронизация внутренних блоков и внешних интерфейсов | BCLK (базовая тактовая частота), REFCLK (опорная частота для PCIe), XTAL_IN/XTAL_OUT (кварцевый генератор) |

| Высокоскоростные линии данных | Прямое подключение к периферийным устройствам без участия чипсета | PCIe lanes (16–24 линии для видеокарты и NVMe-накопителей), процессорные линии памяти (для модулей DDR4/DDR5) |

| Системная магистраль | Связь с чипсетом для доступа к периферийным контроллерам | DMI 4.0 (Intel, до 8 линий), Infinity Fabric (AMD, до 16 линий), связь с южным мостом |

| Управление и мониторинг | Контроль температуры, напряжения, состояния питания | PROCHOT# (сигнал перегрева), SVID (Serial VID для цифрового управления VRM), SMBus (системная шина управления), THERMTRIP# (аварийное отключение) |

| Отладочные и сервисные | Диагностика, программирование микрокода, JTAG-отладка | JTAG (TCK, TMS, TDI, TDO), BMC (базовый системный контроллер), сигналы программирования микрокода |

Замена процессора возможна только при совпадении сокета и совместимости чипсета. Часто производители вводят искусственные ограничения: например, старые чипсеты Z690 формально могут поддерживать 14‑е поколение Intel, но требуют обновления микрокода UEFI, который может отсутствовать в BIOS у бюджетных плат. Таким образом, сокет — это аппаратная граница поколений.

3. Слоты оперативной памяти

Слоты для модулей ОЗУ (DIMM — Dual In-line Memory Module) реализуют точку подключения к высокоскоростной шине памяти, управляемой встроенным в CPU контроллером.

Ключевые аспекты:

- Топология: в современных системах используется T-топология или daisy-chain (зависит от поколения DDR и производителя). При T-топологии сигнал от контроллера разветвляется к двум DIMM на канале — это позволяет гибче настраивать тайминги, но снижает максимальную частоту. Daisy-chain (последовательное соединение) даёт более предсказуемую сигнал-интегрити, но чувствительна к нагрузке от второго модуля.

- Канальность: двухканальный режим активируется при установке модулей в слоты одного цвета (обычно чётные/нечётные). Это удваивает пропускную способность шины памяти, но не ускоряет однопоточные задачи — ускорение проявляется только при параллельном доступе к памяти (например, в СУБД, видеокодировании, виртуализации).

- Поддерживаемые типы: DDR4 и DDR5 физически несовместимы (ключ на модуле смещён), электрически отличаются напряжением (1.2 В vs 1.1 В), частотой тактового сигнала (базовый CLK у DDR4 — до 200 МГц, у DDR5 — до 500 МГц), а также наличием встроенного PMIC (Power Management IC) на модуле DDR5 — он стабилизирует питание локально, что критично при высоких частотах.

Объём слотов не означает, что все они могут использоваться одновременно на максимальной частоте. Например, при четырёх установленных DDR5-модулях частота может снизиться с 6000 МГц до 4800 МГц из-за увеличенной ёмкостной нагрузки на шину.

4. Слоты расширения

Современная материнская плата предоставляет несколько физических форм-факторов для подключения устройств хранения и расширения, но все они, в конечном счёте, используют PCI Express как транспортный протокол — за исключением SATA, который сохраняет собственную шину.

- PCIe-слоты (Peripheral Component Interconnect Express) — это точки подключения к линиям PCIe, выделенным либо процессором, либо чипсетом. Каждая линия (lane) — это дуплексный дифференциальный канал (отправка и приём по отдельным парам проводников). Ширина слота (x1, x4, x8, x16) обозначает максимальное количество линий, но реальное количество может быть ограничено: например, слот x16 может работать в режиме x8, если M.2-слот, подключённый к тем же линиям CPU, активен.

Версии PCIe (3.0, 4.0, 5.0) определяют битрейт на линию:- PCIe 3.0: ~985 МБ/с на линию (x16 ≈ 15.75 ГБ/с)

- PCIe 4.0: ~1.97 ГБ/с на линию (x16 ≈ 31.5 ГБ/с)

- PCIe 5.0: ~3.94 ГБ/с на линию (x16 ≈ 63 ГБ/с)

Пропускная способность всех PCIe-устройств ограничена суммарной шириной линий CPU и PCH.

| Поколение | Год появления | Тип шины | Максимальная пропускная способность | Ключевые особенности |

|---|---|---|---|---|

| ISA | 1981 | Параллельная | 8.33 МБ/с (16-бит) | Первая стандартная шина расширения для IBM PC |

| VLB | 1992 | Параллельная | 132 МБ/с | Прямое подключение к шине процессора 486 |

| PCI 1.0 | 1992 | Параллельная | 133 МБ/с (32-бит/33 МГц) | Независимость от тактовой частоты CPU, поддержка plug-and-play |

| PCI 2.1 | 1995 | Параллельная | 533 МБ/с (64-бит/66 МГц) | Удвоенная разрядность и частота |

| PCI-X 1.0 | 1998 | Параллельная | 1.06 ГБ/с (133 МГц) | Оптимизация для серверных систем |

| PCI-X 2.0 | 2002 | Параллельная | 4.2 ГБ/с (533 МГц) | Квадратная частота, улучшенная синхронизация |

| PCIe 1.0 | 2003 | Последовательная | 250 МБ/с на линию | Полный отказ от параллельной архитектуры |

| PCIe 2.0 | 2007 | Последовательная | 500 МБ/с на линию | Удвоенная тактовая частота кодирования |

| PCIe 3.0 | 2010 | Последовательная | 985 МБ/с на линию | Кодирование 128/130b вместо 8/10b |

| PCIe 4.0 | 2017 | Последовательная | 1.97 ГБ/с на линию | Удвоенная скорость передачи |

| PCIe 5.0 | 2019 | Последовательная | 3.94 ГБ/с на линию | Поддержка устройств с высоким энергопотреблением |

| PCIe 6.0 | 2022 | Последовательная | 7.88 ГБ/с на линию | Переход на импульсно-кодовую модуляцию PAM-4 |

- M.2 — это форм-фактор. Разъём M.2 может поддерживать:

- PCIe ×4 (для NVMe-накопителей, до ~7 ГБ/с в PCIe 4.0);

- SATA (до ~600 МБ/с);

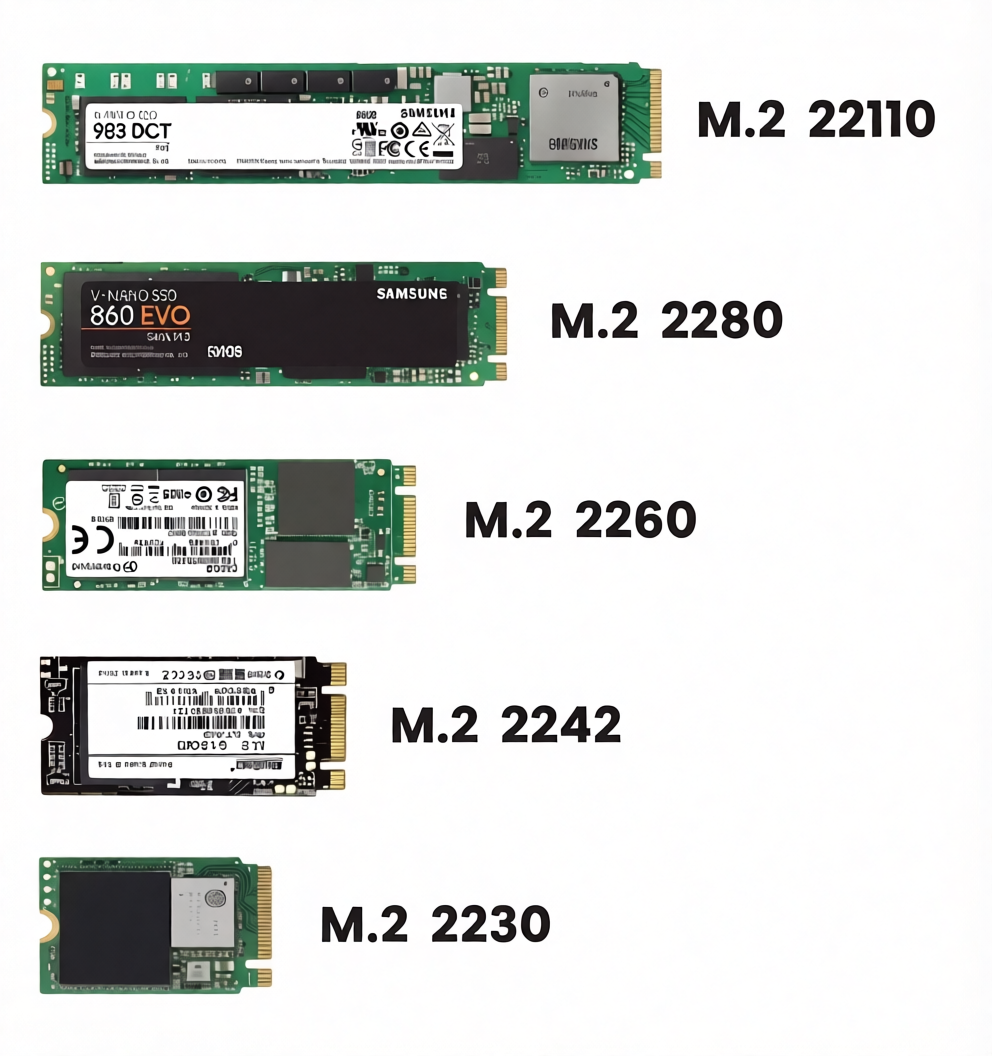

- USB, PCIe ×2, даже Wi-Fi (через спецификацию M.2 Key E или A+E). Ключи (B, M, B+M) определяют, какие сигналы доступны. Например, Key M — это PCIe ×4 + SATA, Key B — SATA + PCIe ×2. Некоторые M.2-слоты используют линии PCIe от чипсета, а не от CPU — это даёт совместимость, но потенциальную задержку и конкуренцию за DMI-шину. M.2 различаются размерами - к примеру, 2230 самый короткий, а 22110 самый длинный:

Размеры плат M.2

| Обозначение | Ширина × Длина, мм | Типичное применение | Максимальное количество чипов памяти |

|---|---|---|---|

| 2230 | 22 × 30 | Беспроводные модули Wi-Fi/Bluetooth, компактные накопители в ультрабуках | 1–2 |

| 2242 | 22 × 42 | Накопители средней ёмкости в тонких ноутбуках и планшетах | 2–4 |

| 2260 | 22 × 60 | Редкий форм-фактор, использовался в ранних моделях гибридных устройств | 4–6 |

| 2280 | 22 × 80 | Стандартный размер для настольных и мобильных накопителей | 8 |

| 22110 | 22 × 110 | Высокоёмкие накопители для рабочих станций и серверов | 16+ |

Цифровое обозначение расшифровывается просто: первые две цифры — ширина в миллиметрах, последние две или три — длина. Плата 2280 имеет ширину 22 мм и длину 80 мм. Некоторые производители используют промежуточные размеры, например 2245 или 2290, но они не получили широкого распространения.

Разъём M.2 содержит вырезы (ключи), определяющие электрическую совместимость и назначение слота. Положение ключа предотвращает установку несовместимого устройства.

| Ключ | Расположение выреза | Поддерживаемые интерфейсы | Типичные устройства |

|---|---|---|---|

| B-key (Socket 2) | Контакты 12–19 | SATA, PCIe ×2, USB 3.0, audio, UART, I²C | SATA SSD, комбинированные накопители |

| M-key (Socket 3) | Контакты 59–66 | PCIe ×4, SATA | Высокоскоростные NVMe накопители |

| B+M key | Оба выреза | SATA, PCIe ×2 | Универсальные накопители с обратной совместимостью |

| A-key | Контакты 8–15 | PCIe ×1, USB 2.0/3.0 | Модули Wi-Fi, WWAN |

| E-key | Контакты 24–31 | PCIe ×1, USB 2.0/3.0, I²C, UART | Расширенные модули беспроводной связи |

Современные материнские платы чаще всего оснащены слотами M-key для накопителей и E-key для беспроводных модулей. Устройства с двойным ключом B+M обеспечивают максимальную совместимость, но работают на скорости интерфейса ×2 вместо ×4.

Физический форм-фактор M.2 не определяет протокол обмена данными. Одно и то же устройство может использовать разные интерфейсы в зависимости от реализации контроллера.

| Протокол | Максимальная пропускная способность | Совместимость с ОС | Типичная задержка |

|---|---|---|---|

| SATA III через M.2 | 600 МБ/с | Полная поддержка всеми операционными системами | 40–60 мкс |

| PCIe 3.0 ×2 | 1.6 ГБ/с | Требуется драйвер для некоторых старых систем | 20–30 мкс |

| PCIe 3.0 ×4 | 3.2 ГБ/с | Стандартная поддержка с Windows 8 / Linux 3.10+ | 15–25 мкс |

| PCIe 4.0 ×4 | 6.4 ГБ/с | Требуется современная ОС и чипсет | 10–20 мкс |

| PCIe 5.0 ×4 | 12.8 ГБ/с | Поддержка с Windows 11 22H2 / Linux 6.0+ | 8–15 мкс |

Устройства, использующие протокол NVMe поверх PCIe, обеспечивают многократное преимущество в скорости произвольного доступа по сравнению с SATA. SATA-накопители в форм-факторе M.2 существуют для сохранения совместимости с устаревшими системами и не дают прироста производительности по сравнению с 2.5-дюймовыми аналогами.

Типы разъёмов на материнской плате

| Тип слота | Физическая длина | Поддерживаемые размеры устройств | Ограничения |

|---|---|---|---|

| Полноценный слот | До 110 мм | 2230, 2242, 2260, 2280, 22110 | Требует места на плате и крепёжного винта |

| Короткий слот | До 80 мм | 2230, 2242, 2260, 2280 | Не принимает устройства 22110 |

| Слот под радиатор | Перекрыт теплораспределительной пластиной | 2280, 22110 | Требует низкопрофильных накопителей или специальных радиаторов |

| Вертикальный слот | Установка перпендикулярно плате | 2280 | Используется в компактных системах |

- SATA (Serial ATA) — устаревающий, но всё ещё востребованный интерфейс, обеспечивающий до 6 Гбит/с (около 550 МБ/с после кодирования 8b/10b). Преимущества: низкая стоимость контроллера, проверенная надёжность, поддержка hot-swap (в серверных версиях), совместимость с HDD. Недостатки: последовательные команды (не параллельные, как NVMe), высокая задержка (до 6 мс у HDD), отсутствие масштабируемости (максимум 6 устройств на чипсет без расширителей).

| Версия | Год стандартизации | Скорость передачи | Пропускная способность | Кодирование | Обратная совместимость |

|---|---|---|---|---|---|

| SATA I (1.5 Гбит/с) | 2003 | 1.5 Гбит/с | 150 МБ/с | 8b/10b | Полная |

| SATA II (3 Гбит/с) | 2004 | 3.0 Гбит/с | 300 МБ/с | 8b/10b | Полная |

| SATA III (6 Гбит/с) | 2009 | 6.0 Гбит/с | 600 МБ/с | 8b/10b | Полная |

| SATA Express | 2013 | 16 Гбит/с (через PCIe) | 1.97 ГБ/с | — | Частичная |

| SATA 3.2 (с поддержкой мультиплексирования) | 2013 | 6 Гбит/с + дополнительные функции | 600 МБ/с | 8b/10b | Полная |

Физические разъёмы и кабели SATA

| Тип разъёма | Назначение | Контактов | Особенности |

|---|---|---|---|

| SATA data (прямой) | Передача данных между контроллером и устройством | 7 | Г-образная форма предотвращает неправильную установку |

| SATA power | Подача питания на устройство | 15 | Комбинирует напряжения +3.3 В, +5 В, +12 В |

| Slimline SATA power | Питание для тонких оптических приводов | 6 | Отсутствует линия +3.3 В |

| Micro SATA (mSATA) | Компактные устройства | 7 данных + 9 питания | Использовался до появления M.2 |

| eSATA | Внешнее подключение | 7 | Усиленный разъём с экранированием, максимальная длина кабеля 2 м |

| eSATAp (Power over eSATA) | Внешнее подключение с питанием | 7 данных + 9 питания | Комбинирует функции eSATA и питания в одном разъёме |

Кабели SATA данных имеют минимальную длину 0.3 м и максимальную 1 м для внутреннего применения. Внешние кабели eSATA допускают длину до 2 м при сохранении целостности сигнала. Экранирование кабеля обязательно для предотвращения помех при высоких скоростях передачи.

Совместимость интерфейсов хранения

| Устройство | Физический интерфейс | Логический протокол | Максимальная скорость |

|---|---|---|---|

| 2.5" SATA SSD | SATA data + power | AHCI поверх SATA | 560 МБ/с |

| M.2 SATA SSD | M.2 B+M key | AHCI поверх SATA | 560 МБ/с |

| M.2 NVMe SSD | M.2 M key | NVMe поверх PCIe | 3.5–7.0 ГБ/с (в зависимости от версии PCIe) |

| mSATA SSD | mSATA | AHCI поверх SATA | 560 МБ/с |

| U.2 SSD | SFF-8639 | NVMe поверх PCIe | 7.0 ГБ/с (PCIe 4.0 ×4) |

Переход от AHCI к NVMe привёл к радикальному снижению задержек и увеличению количества очередей команд. AHCI поддерживает одну очередь глубиной 32 команды, тогда как NVMe предоставляет до 65 535 очередей глубиной по 65 536 команд каждая. Это особенно важно для серверных нагрузок и многопоточных приложений.

5. VRM

Voltage Regulator Module (VRM) — это многофазный импульсный преобразователь напряжения, обеспечивающий стабильное и точно регулируемое питание процессора. Современные CPU потребляют до 350 Вт в пике (например, Intel Core i9-14900K), при этом напряжение ядра колеблется в диапазоне 0.8–1.4 В.

VRM должен:

- преобразовывать 12 В от блока питания в ~1 В с точностью ±25 мВ;

- обеспечивать ток до 200+ А без просадок;

- динамически регулировать напряжение в микросекундном масштабе (в ответ на изменение нагрузки — Loadline Calibration);

- распределять нагрузку между фазами (например, 10+2+1 — 10 фаз для ядер, 2 для кэша, 1 для встроенной графики), чтобы избежать перегрева отдельных компонентов.

Ключевые компоненты VRM:

- PWM-контроллер — «мозг», управляющий скважностью импульсов и синхронизацией фаз;

- драйверы MOSFET — усиливают управляющий сигнал;

- MOSFET-транзисторы (обычно в паре high-side и low-side) — ключевые элементы коммутации;

- дроссели (катушки индуктивности) и конденсаторы — сглаживают пульсации.

Качество VRM напрямую влияет на стабильность разгона, температуру CPU и долговечность системы. Бюджетные платы могут использовать 4‑фазные VRM без радиаторов — при длительной нагрузке это приводит к троттлингу даже без изменения частоты CPU (т.н. VRM throttling).

6. BIOS/UEFI

BIOS (Basic Input/Output System) — устаревший термин. Современные системы используют UEFI (Unified Extensible Firmware Interface) — стандартизированный интерфейс между аппаратным обеспечением и загрузчиком ОС. Его функции:

- POST (Power-On Self-Test) — диагностика базовых компонентов (CPU, RAM, видеокарта), инициализация контроллеров;

- перечисление устройств (enumeration) по шинам PCIe, USB, SATA — построение дерева устройств;

- загрузка микрокода CPU — обновление внутренней микропрограммы процессора до старта ОС (микрокод исправляет аппаратные баги);

- настройка таймингов памяти (XMP/EXPO), напряжений (VDD, VDDQ), частот (BCLK, множителей);

- безопасная загрузка (Secure Boot) — проверка цифровой подписи загрузчика;

- режим совместимости (CSM — Compatibility Support Module) — эмуляция BIOS для старых ОС.

UEFI — это полноценная 32‑ или 64‑битная среда с драйверами устройств, графическим интерфейсом, сетевым стеком (для UEFI-сетевой загрузки) и даже встроенными утилитами (например, Q-Flash у Gigabyte). Размер образа UEFI может превышать 64 МБ, хранится во флеш-памяти SPI (обычно 128–256 МБ), доступной для обновления по USB без ОС.

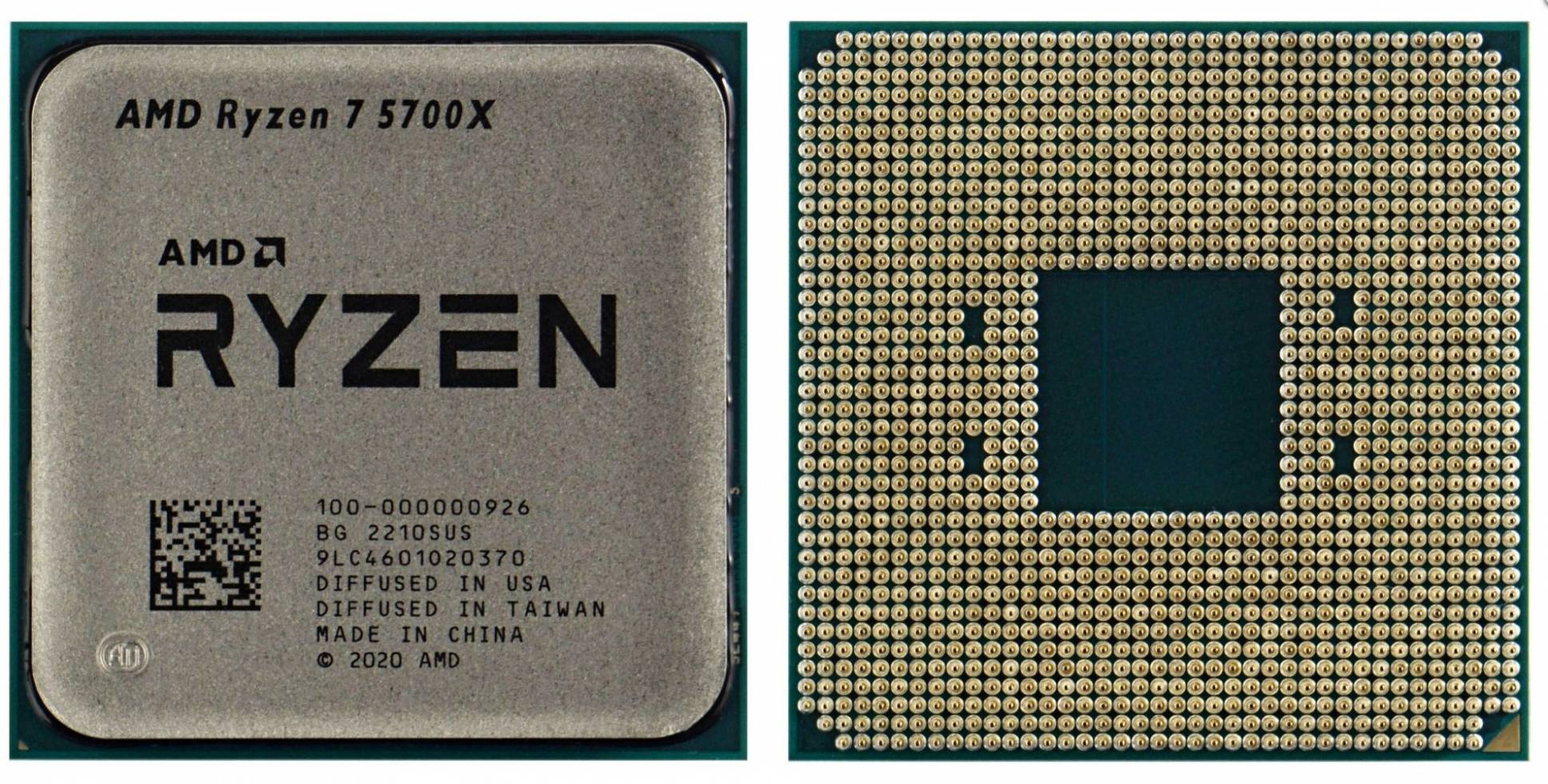

Центральный процессор

Центральный процессор (Central Processing Unit, CPU) — это специализированный конечный автомат, реализованный в кремнии, предназначенный для последовательного (или псевдопараллельного) исполнения машинных инструкций. Его функция — трансляция абстрактных действий («сложить два числа», «перейти по адресу», «сохранить значение в память») в электрические сигналы, управляющие потоками данных между регистрами, кэшами и шинами. Архитектура CPU определяет энергоэффективность, масштабируемость и совместимость с программным стеком.

1. Исполнительный конвейер

Современный CPU работает по принципу конвейерной обработки (pipelining), при котором выполнение одной инструкции разбивается на несколько стадий (stages), а новые инструкции подаются на вход конвейера до завершения предыдущих. Классическая 5‑ступенчатая модель RISC (Fetch → Decode → Execute → Memory Access → Write-back) в x86 реализована в значительно более сложной форме — до 14–19 стадий у Intel Core (например, Sunny Cove или Raptor Cove). Каждая стадия требует строгой синхронизации по тактовому сигналу; сбой на любой стадии (например, промах кэша на стадии Memory Access) приводит к опустошению конвейера (pipeline flush) и потере десятков тактов.

Глубина конвейера — количество стадий, через которые проходит инструкция — значительно выросла с развитием микроархитектур. Увеличение числа стадий позволяет повышать тактовую частоту, так как каждая стадия выполняет меньше работы за такт. Однако чрезмерная глубина повышает штрафы при сбоях предсказания ветвлений.

| Микроархитектура | Год выпуска | Глубина конвейера | Целевая тактовая частота | Особенности реализации |

|---|---|---|---|---|

| Intel Pentium | 1993 | 5 стадий | 60–200 МГц | Простой суперскалярный конвейер |

| Intel Pentium Pro | 1995 | 12 стадий | 150–200 МГц | Первый out-of-order execution в x86 |

| Intel NetBurst (Willamette) | 2000 | 20 стадий | 1.5–2.0 ГГц | Глубокий конвейер для высокой частоты |

| Intel NetBurst (Prescott) | 2004 | 31 стадия | 3.0–3.8 ГГц | Максимальная глубина среди массовых процессоров |

| Intel Core (Merom) | 2006 | 14 стадий | 2.0–2.6 ГГц | Возврат к умеренной глубине после неудачи Prescott |

| Intel Sandy Bridge | 2011 | 14–16 стадий | 2.6–3.8 ГГц | Сбалансированная глубина с улучшенным предсказанием |

| Intel Sunny Cove | 2019 | 17–19 стадий | 3.0–5.0 ГГц | Адаптивная глубина в зависимости от типа инструкции |

| AMD Zen | 2017 | 14 стадий | 3.0–4.0 ГГц | Компактный конвейер с эффективным предсказанием |

| AMD Zen 3 | 2020 | 14 стадий | 3.5–4.9 ГГц | Оптимизация критических путей без увеличения глубины |

Конвейер архитектуры Prescott демонстрировал пределы подхода: при сбое предсказания ветвления терялось до 31 такта, что сводило на нет преимущества высокой частоты. Современные архитектуры находят баланс между глубиной конвейера и штрафами за сбои, часто используя переменную глубину для разных типов инструкций.

Современные x86-процессоры разбивают выполнение инструкции на значительно больше этапов, чем классическая пятиступенчатая модель. Стадии группируются в логические блоки:

| Логический блок | Физические стадии | Основные операции |

|---|---|---|

| Предварительная выборка | 1–3 | Загрузка блоков кода из кэша L1I, распаковка макроинструкций x86 в микрооперации |

| Декодирование | 4–6 | Преобразование x86-инструкций в микрооперации (μop), работа алгоритмов предсказания ветвлений |

| Переименование регистров | 7–8 | Отображение архитектурных регистров на физические для устранения ложных зависимостей |

| Выдача и планирование | 9–10 | Размещение микроопераций в буферах reservation station, ожидание готовности операндов |

| Исполнение | 11–14 | Выполнение арифметических, логических операций в исполнительных блоках (ALU, AGU, FPU) |

| Доступ к памяти | 15–16 | Обращение к кэшу данных L1D, обработка промахов кэша |

| Фиксация результатов | 17–19 | Запись результатов в регистровый файл, обновление состояния процессора в порядке следования программного кода |

Каждая стадия синхронизируется фронтами тактового генератора. Продвижение инструкции на следующую стадию происходит одновременно для всех инструкций в конвейере. Такая строгая синхронизация упрощает проектирование, но делает систему уязвимой к задержкам на любой стадии.

Сбой конвейера возникает при невозможности продолжить обработку инструкций в текущем потоке. Процессор опустошает конвейер — отменяет все находящиеся в нём инструкции — и перезапускает выборку с новой точки кода. Основные причины сбоев:

| Тип сбоя | Триггер события | Типичный штраф в тактах | Механизмы смягчения |

|---|---|---|---|

| Промах предсказания ветвления | Неверное предсказание перехода (if, loop) | 14–19 тактов (Sunny Cove) | Гибридные предикторы, возвратные стеки, обучение на истории |

| Промах кэша L1 | Обращение к данным вне кэша первого уровня | 4–5 тактов до кэша L2, 12+ до памяти | Предварительная выборка (prefetching), неупорядоченный доступ |

| Зависимость по данным | Инструкция ждёт результат предыдущей | 3–5 тактов для простых операций | Переименование регистров, переупорядочивание выполнения |

| Структурная зависимость | Конфликт за исполнительный блок | 1–2 такта | Множественные параллельные исполнительные блоки |

| Исключение или прерывание | Ошибка страницы, деление на ноль | Полная остановка конвейера | Быстрое сохранение состояния, обработка в микрокоде |

Промах предсказания ветвления остаётся наиболее дорогостоящим сбоем в современных архитектурах. Даже при точности предсказания 95% каждые 20 ветвлений приводят к одному сбою, теряя до 20 тактов. Для процессора с частотой 5 ГГц это эквивалентно потере 4 наносекунд на каждое двадцатое ветвление.

Ключевые подсистемы внутри CPU:

-

Front-end (блок выборки и декодирования)

Отвечает за загрузку инструкций из памяти (обычно из L1I-кэша), их декодирование в микрооперации (μops — внутренний RISC-подобный формат Intel/AMD), а также предсказание ветвлений (branch prediction). Современные предикторы используют глобальные и локальные таблицы истории (Global History Buffer, Pattern History Table) и могут достигать точности >95 % — иначе каждый промах по условному переходу стоил бы 10–20 тактов задержки. -

Out-of-Order Execution Engine (движок внеочередного исполнения)

Позволяет выполнять инструкции по мере готовности операндов. Для этого используется:- Reorder Buffer (ROB) — буфер переупорядочения, хранящий μops до их фиксации;

- Reservation Station — очередь готовых к исполнению μops;

- Register Alias Table (RAT) — таблица переименования регистров, исключающая ложные зависимости (WAR/WAW hazards).

Например, если инструкцияADD R1, R2, R3ждёт загрузкиR2из памяти, движок может выполнить последующуюMUL R4, R5, R6, еслиR5иR6уже готовы.

-

Execution Units (исполнительные блоки)

Набор специализированных ALU (арифметико-логических устройств):- Integer ALU — для целочисленных операций (+, –, AND, OR, сдвиги);

- FP/SIMD Unit — для операций с плавающей точкой (FPU) и векторных инструкций (AVX‑512, AVX2);

- Load/Store Unit — управляет доступом к кэшам и шине памяти;

- Branch Unit — фиксирует результаты предсказаний ветвлений.

Современные CPU содержат 4–8 ALU на ядро, 2–4 FP-блока, что позволяет выполнять до 6–8 μops за такт при идеальных условиях.

-

Back-end (блок записи и синхронизации)

Отвечает за фиксацию (retirement) результатов в архитектурные регистры в порядке программы, несмотря на внеочередное исполнение. Только на этой стадии изменения становятся видимыми для других инструкций и ядер.

2. Тактовая частота

Тактовая частота (clock frequency) — это частота основного генератора, синхронизирующего работу логических ячеек CPU. Однако её значение не пропорционально производительности напрямую. Причины:

- IPC (Instructions Per Cycle) — среднее количество инструкций, выполняемых за такт. Два CPU с одинаковой частотой могут отличаться в 2 раза по IPC из-за различий в глубине конвейера, ширине исполнительных блоков, эффективности предсказания ветвлений. Например, архитектура ARM Cortex‑A78 имеет IPC на ~30 % выше, чем A76, при той же частоте.

- Тепловые и энергетические ограничения. Частота динамически регулируется подсистемой DVFS (Dynamic Voltage and Frequency Scaling): при росте нагрузки увеличивается напряжение и частота (boost), при перегреве — снижается (throttling). Пиковая частота (например, 5.8 ГГц у Intel Core i9‑14900K) достигается лишь на 1–2 ядрах на короткий интервал; в многопоточной нагрузке частота падает до 4.0–4.5 ГГц.

- Взаимосвязь с напряжением. Потребляемая мощность растёт пропорционально V²·f (напряжение в квадрате × частота). Повышение частоты на 10 % требует роста напряжения на ~5 %, что даёт рост мощности на ~21 % — нелинейность, ограничивающая масштабируемость.

Таким образом, частота — это управляющий параметр, а не мера мощи. Реальная производительность определяется комбинацией IPC, частоты, количества ядер и эффективности взаимодействия с памятью.

3. Многоядерность и гиперпоточность

Современные CPU содержат от 2 до 128+ ядер. Однако рост числа ядер не гарантирует линейного роста производительности. Ограничивающие факторы:

- Параллелизуемость задачи (закон Амдала). Если 20 % кода последовательно, теоретический максимум ускорения при ∞ ядрах — 5×. Большинство настольных приложений (браузеры, редакторы) имеют параллельность 4–8×.

- Общие ресурсы: кэш последнего уровня (LLC), шина памяти, контроллер PCIe. При 16 ядрах конкуренция за LLC может увеличить latency доступа к данным на 40–60 % по сравнению с 4 ядрами.

- Межъядерная синхронизация: атомарные операции (CAS, LOCK), барьеры памяти (mfence), кэш-когерентность (MESI/MOESI-протоколы) создают задержки при интенсивном обмене данными.

Hyper-Threading (SMT — Simultaneous Multithreading) — технология, позволяющая одному физическому ядру выполнять 2 (редко — 4) потока инструкций одновременно. Это достигается за счёт:

- дублирования архитектурных состояний (регистров, ROB, RAT);

- совместного использования исполнительных блоков, кэшей и шин.

Эффект: при не насыщенных исполнительных блоках (например, поток ждёт данных из памяти) второй поток может использовать простаивающие ALU. Прирост производительности — 15–30 % в многопоточных, нечувствительных к latency задачах (кодирование видео, рендеринг); в высокочастотных, latency-критичных сценариях (HFT, low-latency gaming) SMT может снизить производительность из-за конкуренции за ресурсы.

4. Иерархия кэш-памяти

Кэш-память — это высокоскоростная статическая память (SRAM), встроенная в кристалл CPU, предназначенная для сокращения latency доступа к данным по сравнению с DRAM (ОЗУ). Архитектура кэшей строится по принципу вложенности (inclusive/exclusive policies) и локальности (пространственной и временной).

Типичная иерархия у x86 (на примере Intel Core):

-

L1 (Level 1)

- Разделяется на L1I (инструкции) и L1D (данные), по 32–48 КБ на ядро;

- Latency: 3–5 тактов;

- Ассоциативность: 8-way set associative;

- Физически находится в непосредственной близости от исполнительных блоков.

-

L2 (Level 2)

- Единый кэш на ядро (512 КБ – 2 МБ);

- Latency: 10–14 тактов;

- Часто exclusive по отношению к L1 (данные в L2 отсутствуют в L1), что увеличивает эффективную ёмкость.

-

L3 (Level 3, Last-Level Cache, LLC)

- Общий для всех ядер (16–128 МБ);

- Latency: 30–60 тактов (зависит от количества ядер и топологии кристалла);

- Реализован как sliced cache: каждый «кусок» физически привязан к определённому кластеру ядер (например, в Intel CCD — 8 ядер + 32 МБ L3), а доступ «чужому» slice’у идёт через межсоединение (ring bus или mesh).

- Используется для кэширования страниц таблицы трансляции (TLB misses → page walks → L3 cache hits).

Ключевой параметр — miss rate (частота промахов). Даже 1 % промахов в L3 приводит к обращению к DRAM с latency ~100 нс (≈300 тактов при 3 ГГц), что в 50–100 раз медленнее L1. Таким образом, кэши — это механизм смягчения асимметрии скоростей: без них современные CPU простаивали бы >90 % времени.

- L1 — карманы на фартуке: самые быстрые, но вмещают лишь пару ингредиентов;

- L2 — полка над плитой: чуть дальше, но уже целая тарелка специй;

- L3 — общий холодильник на кухне: до него идти дольше, но там хранятся все основные продукты.

Если нужного ингредиента нет в кармане, повар проверяет полку, потом холодильник. Только если и там нет — идёт в кладовую (оперативная память).

Кэш-промах — это как поиск ключей от машины. Вы проверяете карман (L1) — нет. Смотрите на полке у входа (L2) — тоже нет. Заглядываете в ящик тумбочки (L3) — опять нет. Тогда вы идёте в гараж (оперативная память), где ключи лежат в коробке с другими вещами. Поиск в гараже занимает 50 раз дольше, чем проверка кармана. Современные программы стараются «класть ключи всегда в карман», чтобы избежать таких походов.

5. Взаимодействие с внешним миром

CPU не существует изолированно. Его производительность лимитируется скоростью обмена данными:

-

Шина памяти (Memory Bus)

Управляется встроенным Memory Controller (с 2003 г. у AMD, с 2008 г. у Intel). Современные контроллеры поддерживают двухканальный (dual-channel) и четырёхканальный (quad-channel) режимы, что удваивает/учетверяет пропускную способность. Однако latency остаётся высоким (~60–80 нс), и его нельзя «ускорить» частотой — только уменьшением физического расстояния (HBM, 3D-stacking). -

PCIe-интерфейс

CPU предоставляет «корневые» линии PCIe (обычно 16–24), напрямую подключённые к видеокарте и первому M.2-слоту. Эти линии обходят чипсет, что снижает latency и избавляет от конкуренции за DMI-шину. В серверных CPU (AMD EPYC, Intel Xeon Scalable) количество линий достигает 128 (PCIe 5.0), что позволяет строить системы с 8+ GPU без бутылочного горлышка. -

Когерентность кэшей (Cache Coherence)

При наличии нескольких CPU (multiprocessor) или NUMA-узлов (Non-Uniform Memory Access) требуется протокол, гарантирующий согласованность данных в кэшах. Используется MESI (Modified, Exclusive, Shared, Invalid) или его расширения (MOESI, MESIF). Например, при записи в ядре A данные в ядре B автоматически инвалидируются (Invalidate), либо передаются напрямую (Cache-to-Cache transfer), если поддерживаются.

Оперативная память

Оперативная память (Random Access Memory, RAM) — это энергозависимое полупроводниковое устройство хранения, предназначенное для обеспечения процессора и его подсистем (например, встроенной графики) данными и инструкциями с минимальной задержкой. Несмотря на кажущуюся простоту функции — «временное хранилище» — RAM является центральным звеном в системе балансировки скорости, ёмкости и стоимости. Её архитектура определяет latency-чувствительность всей вычислительной системы.

1. Физическая основа

Современная ОЗУ реализована на основе динамической памяти с произвольным доступом (DRAM — Dynamic RAM). В отличие от статической памяти (SRAM, используемой в кэшах), DRAM хранит бит информации в виде электрического заряда на конденсаторе, управляемого одним транзистором (1T1C-ячейка). Эта конструкция обеспечивает высокую плотность упаковки (до 16 Гбит на чип у DDR5), но вводит фундаментальное ограничение: заряд конденсатора со временем утекает.

Поэтому DRAM требует периодического обновления (refresh) — процесса, при котором контроллер памяти считывает заряд каждой строки (row) и записывает его обратно, восстанавливая уровень. Интервал обновления стандартизирован: JEDEC требует полного обновления всех строк за 64 мс. При частоте 3200 МГц это означает, что ~1 % тактов тратится на refresh-циклы — невидимая, но реальная «налоговая» нагрузка на пропускную способность.

Структура банка памяти (bank) устроена иерархически:

- Чип (die) → объединяется в ранг (rank) (обычно 8 чипов для 64‑битной шины + 8 бит ECC);

- Ранг состоит из банков (banks) — независимых матриц;

- Банк — это двумерная матрица строк (rows) и столбцов (columns);

- Строка — группа ячеек, активируемая одновременно (page);

- Столбец — отдельный бит в строке.

Доступ к данным происходит по принципу RAS → CAS (Row Address Strobe → Column Address Strobe):

- Активация строки (Activate) — открытие «страницы» в банке (latency: tRCD);

- Чтение/запись столбца (Read/Write) — выбор данных внутри страницы (latency: tCAS);

- Предзарядка (Precharge) — закрытие строки для последующей активации (latency: tRP).

Если следующий запрос адресован той же строке, этап 1 и 3 пропускается — это page hit, и latency падает в 2–3 раза. Именно поэтому современные аллокаторы памяти (например, jemalloc) стремятся к пространственной локальности: размещение связанных данных в пределах одной страницы DRAM.

2. DDR-интерфейс

Современные модули ОЗУ используют интерфейс DDR (Double Data Rate) — передачу данных по обоим фронтам тактового сигнала (rising и falling edge). Это позволяет удвоить эффективную частоту без увеличения тактовой частоты шины. Например, DDR4‑3200 имеет базовую частоту 1600 МГц, но передаёт 3200 MT/s (MegaTransfers per second).

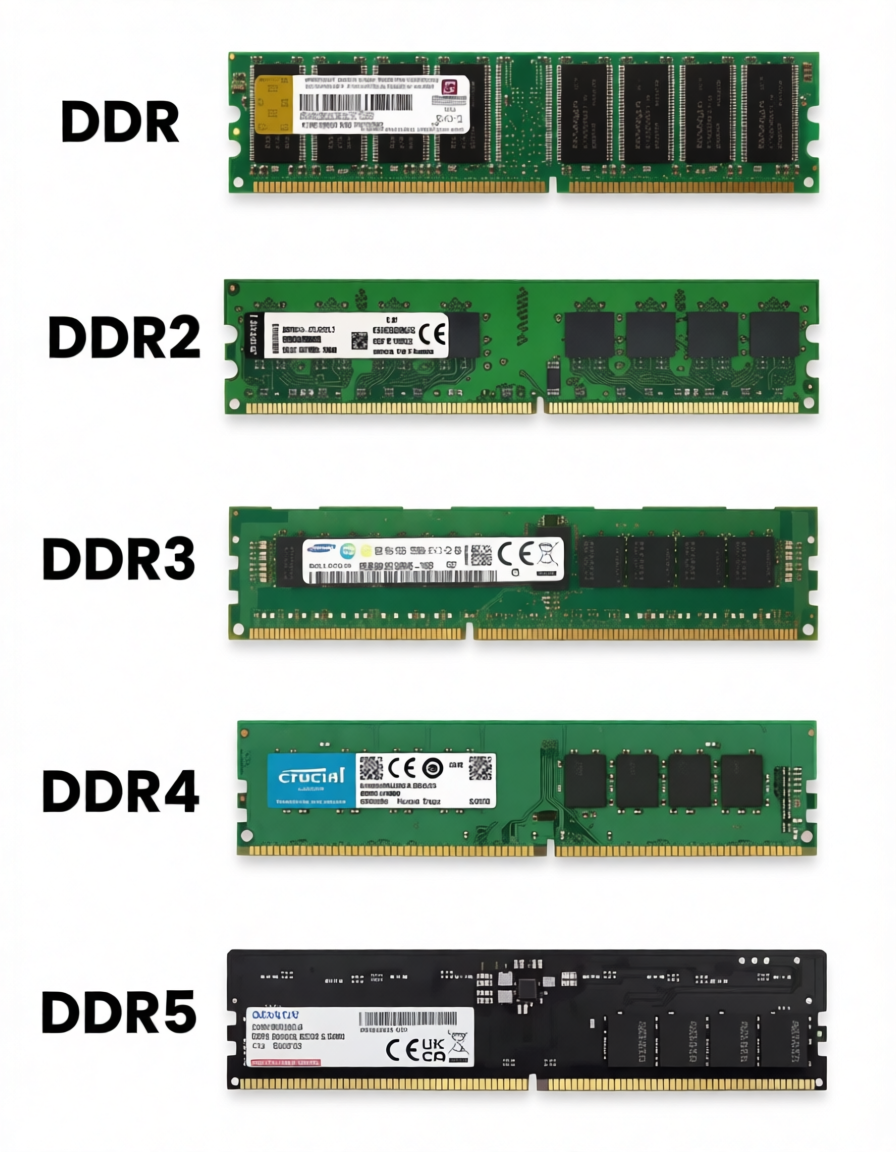

Вот так выглядят различные типы оперативной памяти:

Ключевые поколения и их различия:

| Параметр | DDR3 | DDR4 | DDR5 |

|---|---|---|---|

| Напряжение (VDD) | 1.5 В (1.35 В LV) | 1.2 В | 1.1 В |

| Базовая частота | до 1066 МГц | до 1600 МГц | до 5000 МГц (JEDEC) |

| Эффективная частота | до 2133 МТ/с | до 3200 МТ/с | до 6400 МТ/с (и выше) |

| Ширина шины | 64 бит | 64 бит | 64 бит (но разделена на 2×32) |

| Чипы на ранг | 8 | 8 | 8 (но с x8/x16 организацией) |

| Архитектура банка | 8 банков | 16 банков | 32 банков (8 групп × 4) |

| Управление питанием | Внешнее (на плате) | Внешнее | PMIC на модуле (12 В → 1.1 В) |

Особенности DDR5:

- Двухканальный режим на уровне модуля: каждый модуль DDR5 разделяет 64‑битную шину на два независимых 32‑битных канала (с отдельными командными шинами), что улучшает параллелизм и снижает нагрузку на контроллер.

- On-Die ECC: коррекция ошибок на уровне чипа (не путать с системным ECC), что повышает надёжность без потери производительности.

- Adaptive Refresh Management (ARM): динамическая настройка частоты refresh в зависимости от температуры (при +85°C refresh учащается в 2 раза).

3. Тайминги

Тайминги (например, 16‑18‑18‑36) — реальные задержки в тактах, определяемые физическими свойствами DRAM. Расшифровка основных:

- tCL (CAS Latency) — задержка между командой чтения и появлением первых данных;

- tRCD (RAS to CAS Delay) — время между активацией строки и доступом к столбцу;

- tRP (Row Precharge Time) — время закрытия строки;

- tRAS (Row Active Time) — минимальное время, в течение которого строка должна оставаться открытой.

- Первый едет медленно (60 км/ч), но возит по одной коробке каждые 15 секунд.

- Второй мчится (120 км/ч), но загружает коробку только каждые 18 секунд.

Хотя второй грузовик быстрее, его «задержка между отправками» чуть выше. Однако за час он доставит вдвое больше коробок — потому что скорость компенсирует паузу. Так работает память: высокая частота снижает абсолютную задержку, даже если тайминги в тактах растут.

При увеличении частоты тайминги в тактах растут, но их абсолютное значение в наносекундах может снижаться. Например:

- DDR4‑2133, tCL=15

→15 / (2133/2)≈14.07 нс - DDR4‑3600, tCL=18

→18 / (3600/2)≈10.00 нс

Таким образом, более «высокие» тайминги при высокой частоте могут давать меньшую latency, чем низкие при низкой частоте. Оптимальное соотношение определяется bandwidth-latency trade-off: для игровых и интерактивных приложений важнее низкая latency, для HPC и СУБД — высокая пропускная способность.

4. Роль в системной архитектуре

RAM — это активный участник управления памятью. Современные ОС используют её в связке с MMU (Memory Management Unit) для реализации:

- Виртуальной памяти: отображение виртуальных адресов (48‑ или 57‑битных) в физические через многоуровневые таблицы страниц (page tables);

- Copy-on-Write (CoW): при fork() дочерний процесс разделяет страницы с родителем до первой записи;

- Memory-mapped I/O: отображение файлов в адресное пространство процесса (mmap), что устраняет копирование через буферы ядра.

На многосокетных системах (серверы) возникает модель NUMA (Non-Uniform Memory Access): каждый CPU имеет локальную память (через свой контроллер) и удалённую (через межпроцессорное соединение — Infinity Fabric, UPI). Доступ к удалённой памяти может быть в 1.5–2.5 раза медленнее. ОС и приложения (например, PostgreSQL, SAP HANA) должны учитывать топологию NUMA при размещении потоков и данных.

5. Взаимодействие с CPU

Встроенный в CPU Memory Controller (IMC) — это ASIC, отвечающий за:

- преобразование логических запросов (load/store) в последовательность RAS/CAS-команд;

- арбитраж запросов от ядер, PCIe-устройств (DMA), встроенной графики;

- балансировку нагрузки между рангами и банками;

- поддержку режимов (single/dual/quad-channel), ECC, XMP/EXPO.

Пропускная способность (bandwidth) определяется по определённой формуле. Однако реальная пропускная способность в приложениях редко превышает 70–80 % от теоретической из-за:

- неоптимальных паттернов доступа (random vs sequential);

- bank conflicts (запросы к одному банку подряд);

- refresh overhead (дополнительная нагрузка на процессов);

- задержек контроллера.

latency памяти — основной лимитер производительности в latency-bound приложениях (компиляторы, интерпретаторы, OLTP-базы данных). Уменьшение tCAS с 18 до 14 при той же частоте может дать прирост до 8 % в таких сценариях — без изменения IPC или тактовой частоты CPU.

bound - это граница, а latency - это задержка. latency-bound - ограниченные задержкой.

6. Энергетика и надёжность

Оперативная память — второй по потреблению компонент после CPU и GPU. DDR5 снижает напряжение, но увеличивает количество чипов и частоту, поэтому суммарное потребление может быть сопоставимо с DDR4. В серверных системах используется:

- ECC (Error-Correcting Code) — 8 дополнительных бит на 64‑битное слово, позволяющие исправлять однобитовые ошибки и обнаруживать двухбитовые (SECDED — Single Error Correction, Double Error Detection);

- Chipkill — расширенная ECC, выдерживающая сбой целого чипа в ранге;

- Memory Patrol Scrubbing — фоновое сканирование памяти на ошибки.

В потребительских системах ECC обычно отсутствует, что делает их уязвимыми к soft errors (вызванным космическими лучами или альфа-частицами) — частота ~1 ошибка на 256 ГБ·год при уровне моря. Для критических приложений это недопустимо.